October 10, 2009

Jeremy Roberson, Esteban Valles, Konstantin Tarasov, Eugene Grayver, Kevin King Digital Communication Implementation Department, Communication Systems Implementation Subdivision

Prepared for:

GOES-R Program Office National Oceanic and Atmospheric Administration

Contract No. DG133E07CQ005

Authorized by: Civil and Commercial Operations

Approved for public release.

October 10, 2009

Jeremy Roberson, Esteban Valles, Konstantin Tarasov, Eugene Grayver, Kevin King Digital Communication Implementation Department, Communication Systems Implementation Subdivision

Prepared for:

GOES-R Program Office National Oceanic and Atmospheric Administration

Contract No. DG133E07CQ005

Authorized by: Civil and Commercial Operations

Approved for public release.

October 10, 2009

Jeremy Roberson, Esteban Valles, Konstantin Tarasov, Eugene Grayver, Kevin King Digital Communication Implementation Department, Communication Systems Implementation Subdivision

Prepared for:

GOES-R Program Office National Oceanic and Atmospheric Administration

Contract No. DG133E07CQ005

Authorized by: Civil and Commercial Operations

Approved for public release.

| Approved by: | A۱ | opr | ove | edi | bv | : |

|--------------|----|-----|-----|-----|----|---|

|--------------|----|-----|-----|-----|----|---|

Philip A. Dafesh, Director

Digital Communication Implementation

Department

Communication Systems Implementation

Subdivision

Communications and Networking Division

Engineering and Technology Group

M. Christian Wallisch, Systems Director GOES-R and NOAA Architecture Support Civil and Commercial Operations

All trademarks, service marks, and trade names are the property of their respective owner

# Contents

| 1. | Introd     | luction                                               | 1   |

|----|------------|-------------------------------------------------------|-----|

| 2. | EMW        | TN/HRIT Prototype Solution Description                | 3   |

|    | 2.1        | System Overview                                       |     |

|    | 2.2        | Hardware Overview                                     |     |

|    |            | 2.2.1 AID Front End                                   |     |

|    |            | 2.2.2 AID Power Meter                                 |     |

|    |            | 2.2.3 Power Consumption                               |     |

|    | 2.3        | Software Overview                                     |     |

| 3. | Hardy      | vare Description and Performance                      | 9   |

|    | 3.1        | Hardware Design                                       |     |

|    |            | 3.1.1 AID: Power Circuit                              |     |

|    |            | 3.1.2 AID: Clocking Circuit                           | 9   |

|    |            | 3.1.3 AID: Signal Circuit                             | 9   |

|    | 3.2        | Hardware Performance                                  | 15  |

| 4. | Softw      | are Description                                       | 17  |

|    | 4.1        | Software Framework                                    |     |

|    | 4.2        | Frequency Acquisition                                 | 19  |

|    | 4.3        | LRIT Transmitter Specifications                       |     |

|    |            | 4.3.1 LRIT Transmission Process                       | 21  |

|    | 4.4        | LRIT Software Receiver Architecture                   | 22  |

|    | 4.5        | EMWIN-N Transmission Specifications                   | 25  |

|    |            | 4.5.1 EMWIN-N Transmission Process                    | 25  |

|    | 4.6        | EMWIN-N Software Receiver Architecture                | 26  |

|    | 4.7        | Soft-Decision Viterbi Decoder                         |     |

|    | 4.8        | EMWIN-I Signal Specifications                         |     |

|    | 4.9        | EMWIN-I Software Receiver Architecture                |     |

|    |            | 4.9.1 Symbol Timing Acquisition                       |     |

|    |            | 4.9.2 Symbol Timing-Tracking                          |     |

|    | 4.10       | The Data Link Layer                                   |     |

|    |            | 4.10.1 EMWIN-N, HRIT and LRIT CCSDS Packet Processing |     |

|    |            | 4.10.2 EMWIN-N Data Socket Output                     |     |

|    |            | 4.10.3 HRIT and LRIT Data Socket Output               |     |

|    |            | 4.10.4 EMWIN-I Data Link Layer Processor              |     |

|    |            | 4.10.5 EMWIN-I Data Socket Output                     | 3 / |

| 5. | <b>EMW</b> | TN/HRIT Prototype Solution Performance                |     |

|    | 5.1        | Noise Performance                                     |     |

|    |            | 5.1.1 Testing Methodology                             |     |

|    |            | 5.1.2 Noise Performance Results                       |     |

|    |            | 5.1.3 GOES-R Frequency Plan Noise Performance Tests   |     |

|    | 5.2        | Throughput                                            | 52  |

| 6. | Concl      | usion                                                 | 55  |

| 7. | Acror      | ıym List                                              | 57  |

| 8. | Biblio     | ography                                               | 59  |

| Appendix A | A. Software Design Document                                                                         | 61        |

|------------|-----------------------------------------------------------------------------------------------------|-----------|

| Appendix I | B. Hardware Implementation                                                                          | 69        |

|            | Figures                                                                                             |           |

| Figure 1.  | EMWIN/HRIT system diagram.                                                                          | 4         |

| Figure 2.  | LED example.                                                                                        |           |

| Figure 3.  | Detailed EMWIN/HRIT system diagram.                                                                 | 7         |

| Figure 4.  | AID diagram.                                                                                        |           |

| Figure 5.  | SAW filter frequency response.                                                                      |           |

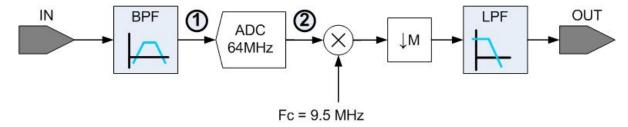

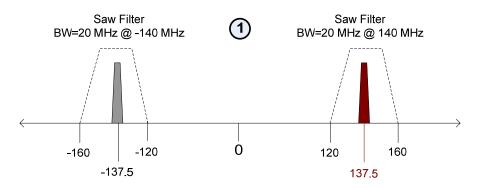

| Figure 6.  | IF-Sampling block diagram.                                                                          |           |

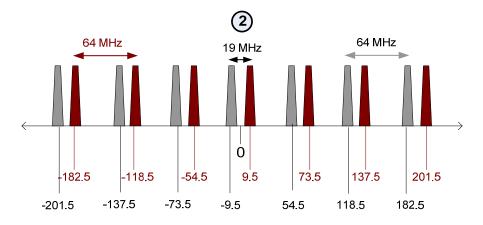

| Figure 7.  | IF Sampling Signal 1.                                                                               |           |

| Figure 8.  | IF Sampling Signal 2.                                                                               | 11        |

| Figure 9.  | Spectrum of GOES-R image using 48 MHz sampling. The HRIT signals are interfering                    | 12        |

| Figure 10. | Spectrum of GOES-R image using 64 MHz sampling. The HRIT signals are not interfering.               | 13        |

| Figure 11. | FPGA digital down-converter implementation.                                                         | 15        |

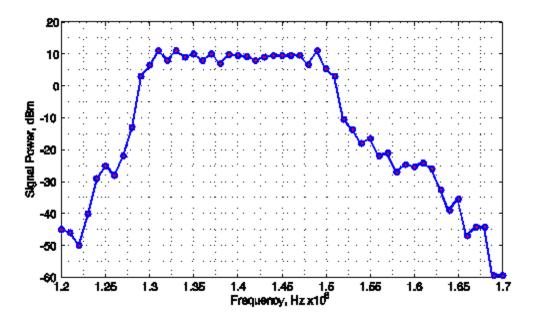

| Figure 12. | Spectrum of live GOES-12 signal                                                                     | 16        |

| Figure 13. | Overall EMWIN/HRIT system block diagram.                                                            | 18        |

| Figure 14. | Block diagram of software-based frequency acquisition.                                              | 20        |

| Figure 15. | The LRIT and EMWIN-OQPSK packet structure.                                                          | 23        |

| Figure 16. | Block diagram showing the different signal processing blocks in an                                  |           |

|            | LRIT BPSK receiver.                                                                                 | 25        |

| Figure 17. | Block diagram showing the different signal processing blocks in an                                  |           |

|            | EMWIN OQPSK receiver                                                                                |           |

| -          | Down-converted FSK Frequency Diagram                                                                | 29        |

| Figure 19. | Block diagram showing the different signal processing blocks in an EMWIN-I FSK receiver             | 30        |

| Figure 20. | Detailed diagram of FSK timing acquisition block.                                                   |           |

| Figure 21. | Detailed diagram of FSK symbol timing block.                                                        | 33        |

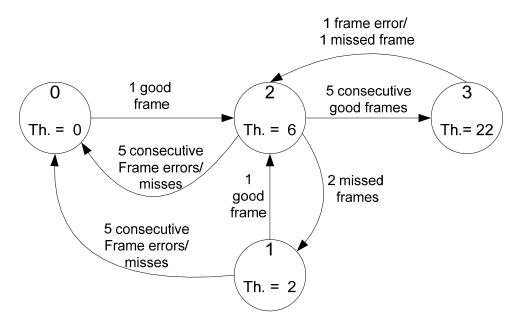

| Figure 22. | CADU Frame synchronization lock state graph.                                                        |           |

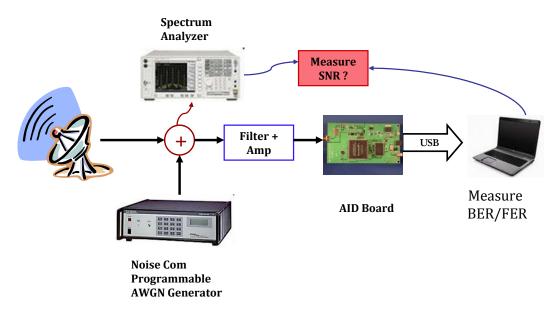

| Figure 23. | Testing setup for live signal feed experiment.                                                      |           |

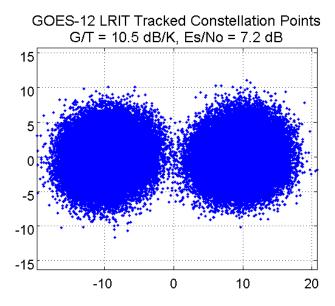

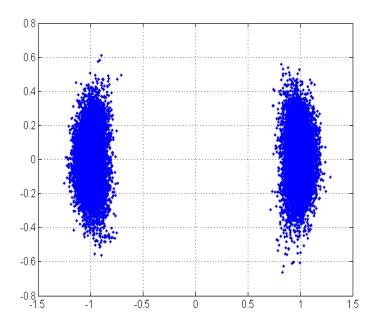

|            | LRIT constellation points.                                                                          |           |

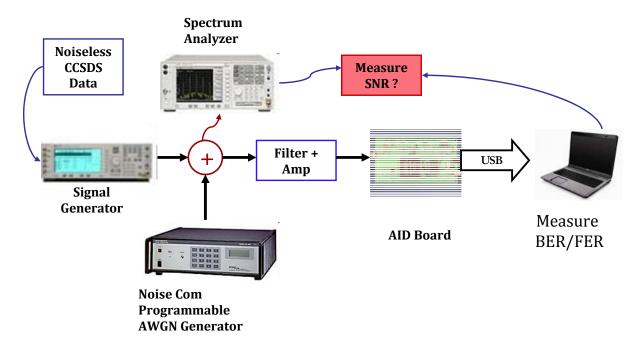

|            | Diagram of signal generator testing setup.                                                          |           |

|            | Diagram of testing using a file source.                                                             |           |

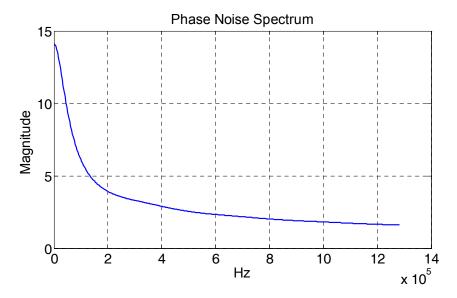

| -          | Phase noise spectrum of waveform generated by a file source.                                        |           |

|            | File source based LRIT signal with 16° of phase noise and SNR = 20 dB.                              |           |

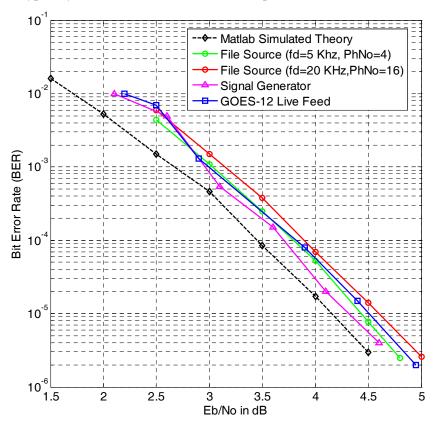

| •          | LRIT BER Performance Test Results Using All Test Methodologies                                      |           |

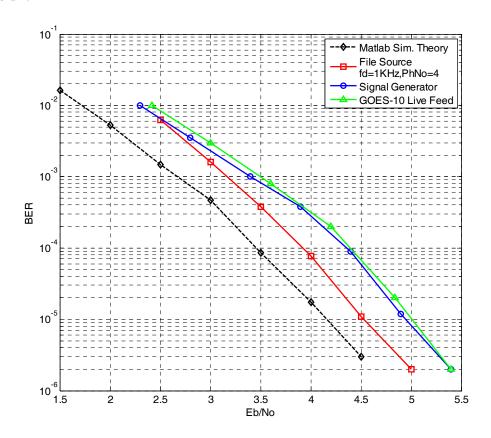

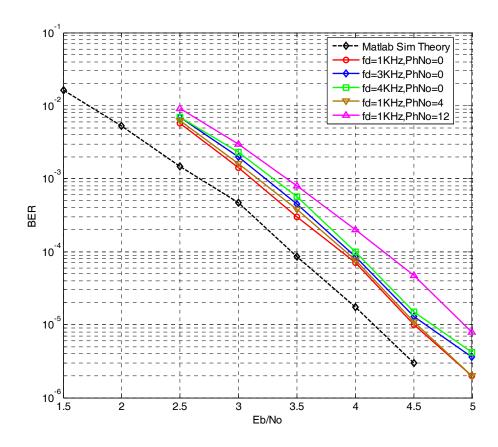

| Figure 30. | EMWIN-N bit error rate test results using all test methodologies                                    | 47        |

| Figure 31. | EMWIN-N BER performance comparison using file sources with varying levels of                        |           |

| г. 22      | RF impairments                                                                                      | 48        |

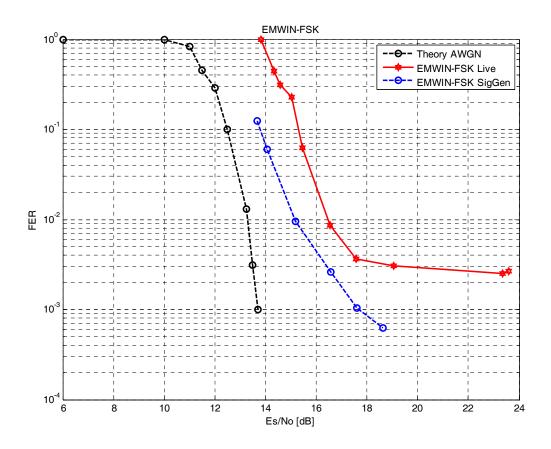

| Figure 32. | EMWIN-I (FSK) Frame Error Rate (FER) performance over GOES-12 compared to                           | <i></i> 0 |

| Eigene 22  | an ideal FSK modulation over AWGN noise. Packet size is 8128 bits.                                  | 50        |

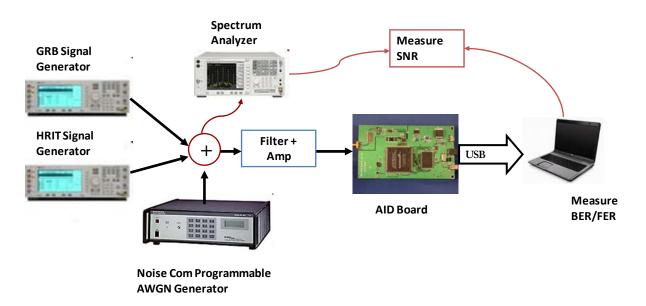

| Figure 33: | Diagram of GOES-R frequency emulation testing setup including HRIT and GRB signals using AID board. | 51        |

| Figure 34. | Spectrum analyzer screen capture of the input HRIT + GRB signal including |    |

|------------|---------------------------------------------------------------------------|----|

|            | noise and SAW filter response.                                            |    |

| Figure 35. | 3                                                                         |    |

|            | AID board layout.                                                         |    |

| Figure 37. | Aerospace RF (L-band) digitizer board block diagram                       | 76 |

|            | Tables                                                                    |    |

| Table 1.   | Signals of Interest from NOAA's GOES Satellites                           | 1  |

| Table 2.   | AID Specifications                                                        | 4  |

| Table 3.   | AID List of Major Components                                              |    |

| Table 4.   | Software Specifications                                                   |    |

| Table 5.   | EMWIN/LRIT Configuration                                                  | 14 |

| Table 6.   | AID User-Defined Input Parameters                                         |    |

| Table 7.   | Configuration for Frequency-Acquisition Subroutine                        | 20 |

| Table 8.   | Key LRIT Transmission Parameters                                          | 22 |

| Table 9.   | Soft Decision Viterbi Decoding Parameters                                 | 25 |

| Table 10.  | EMWIN-N Key Parameters                                                    | 26 |

| Table 11.  | EMWIN-I Key Parameters                                                    | 29 |

| Table 12.  | LRIT Frame Error Rate Performance for all Testing Methodologies           | 46 |

| Table 13.  | EMWIN-N FER Performance Over GOES-10 Live Feed and                        |    |

|            | Signal Generator Testing                                                  | 48 |

| Table 14.  | EMWIN-N FER Performance Using a File Source with Varying Levels of        |    |

|            | Drift Rate with a Fixed Phase Noise of 4°                                 | 49 |

| Table 15.  | EMWIN-N FER Performance Using a File Source with Varying Levels of        |    |

|            | Phase Noise with a Fixed Drift of 1 KHz                                   | 49 |

| Table 16.  | Throughput Measurements for EMWIN-N and LRIT                              | 53 |

| Table 17.  | Component List and Prices                                                 | 70 |

|            |                                                                           |    |

#### 1. Introduction

The Geostationary Operational Environmental Satellite R-series (GOES-R) program [1] is a collaborative development and acquisition effort between the National Oceanic and Atmospheric Administration (NOAA) and the National Aeronautics and Space Administration (NASA). There are many signals of interest transmitted on the GOES satellite constellation [2]. This document focuses on two signals in particular, the Emergency Managers Weather Information Network Signal (EMWIN) [3][4], and the Low Rate Information Transmission, or LRIT [and its follow-on in the GOES-R era, High Rate Information Transmission (HRIT)] [5][6].

In the current GOES I-M era, EMWIN-I (FSK modulated) and LRIT are being transmitted over the GOES-11 (West) and GOES-12 (East) satellites (Table 1). In the GOES N-O-P era, the EMWIN-N signal will be transmitted on GOES-13 through GOES-15. The EMWIN-I and LRIT signals have their own carriers but share transponders, while the EMWIN-N and LRIT signals have their own transponders. There are commercially available EMWIN receivers currently available [7].

In the GOES-R era, the EMWIN and LRIT information bit-stream will be combined before signal modulation and transmission. The new LRIT signal, with embedded EMWIN, will have a transmission baud rate of 927 kilo symbols-per-second (ksps). Because the new combined signal will be at a higher rate, its name will be changed from LRIT (from the GOES N/O/P era) to HRIT in the GOES-R era.

|             | Launch    |                |                    | Throughput    |

|-------------|-----------|----------------|--------------------|---------------|

| Spacecraft  | Year      | Signal         | Modulation         | [sps]         |

| GOES-I (8)  | 1994      | WEFAX          | FSK                | 9600          |

| GOES-J (9)  | 1995      | WEFAX          | FSK                | 9600          |

| GOES-K (10) | 1997      | EMWIN-N        | OQPSK <sup>2</sup> | 17,970        |

| GOES-L (11) | 2000      | EMWIN-I / LRIT | FSK / BPSK         | 9600 /293,000 |

| GOES-M (12) | 2001      | EMWIN-I / LRIT | FSK / BPSK         | 9600 /293,000 |

| GOES-N (13) | 2006      | EMWIN-N / LRIT | OQPSK / BPSK       | 17,970 /      |

|             |           |                |                    | 293,000       |

| GOES-O (14) | 2009      | EMWIN-N / LRIT | OQPSK / BPSK       | 17,970 /      |

|             |           |                |                    | 293,000       |

| GOES-P (15) | 2010      | EMWIN-N / LRIT | OQPSK / BPSK       | 17,970 /      |

|             |           |                |                    | 293,000       |

| GOES-Q (16) | Cancelled |                |                    |               |

| GOES-R (17) | 2014      | HRIT           | BPSK               | 927,000       |

Table 1. Signals of Interest from NOAA's GOES Satellites

The current EMWIN and LRIT receivers will not be able to receive the transmission off of GOES-R when the signal goes active, thus motivating the design of a low-cost EMWIN/HRIT prototype receiver that maintains the spirit of the EMWIN service of maximum accessibility. The prototype receiver can be used now to receive the current EMWIN and LRIT signal, and will be capable of receiving the GOES-R HRIT transmission without any changes to the major components of the system, making it an ideal solution to ease the transition. The prototype is not intended to be commercially available, but rather lay the groundwork for a commercial product lines.

This document is primarily intended for developers and covers system, hardware, and software design considerations. It is important to note how this document is organized before reading further.

<sup>1</sup> The name HRIT implicitly refers to both the HRIT and EMWIN data-streams.

<sup>2</sup> The GOES-K satellite was updated to transmit the EMWIN-N (OQPSK) signal.

Section 2 presents an overview of the product description. The main hardware and software blocks are introduced. In Section 3, a detailed explanation of the hardware component of the proposed solution is presented. Similar analysis is done for the software components in Section 4. Performance results for the integrated receiver are presented in Section 5. Software and hardware appendices with detailed information for future developers appear in Sections 6 and 7. Conclusions are presented in Section 8.

# 2. EMWIN/HRIT Prototype Solution Description

# 2.1 System Overview

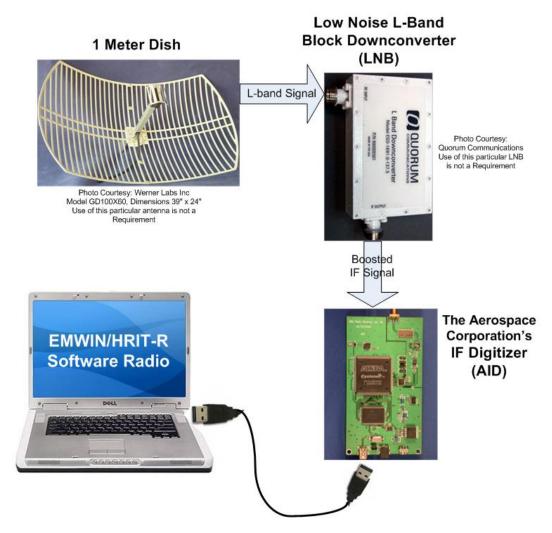

The EMWIN/HRIT prototype receiver is a software-based radio that is designed around an open source framework called GNURadio [8][9]. (An EMWIN-I and EMWIN-N solution designed by Avtec is also a software based radio [10].) Most of the receiver is implemented in software running on a Windows-based PC. However, there is some additional hardware required for the system to work. Figure 1 shows an example of the complete solution. Every system requires a powered satellite dish that is at least 1 meter. Such dishes are commercially available for as low as \$500 [11]. All EMWIN-I/N users that currently have a dish will not be required to purchase a new one to receive HRIT. The dish is followed by a Low Noise Block (LNB) Down-converter that amplifies the signal and down-converts from L-band (~1690 MHz) to an IF frequency around 140 MHz. The Gain over Temperature (G/T) Figure of Merit (FOM) of the combined dish and LNB/LNA<sup>3</sup> must be at least -0.3 dB/K.

The bandwidth of EMWIN-I/N is a narrowband signal that allows existing commercial receivers to utilize a PC's sound-card to digitize the data and send it to the computer for further demodulation. The new HRIT signal's bandwidth is too wide for any typical PC component to digitize the signal. New hardware is therefore required with the sole purpose of digitizing the analog signal and streaming the data to the computer for further processing.

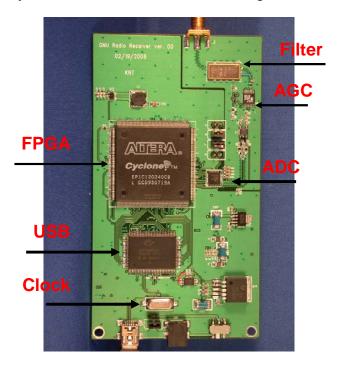

Currently, there exists a commercially available device called the Universal Software Radio Peripheral (USRP) designed by Ettus Research LLC that is capable of digitizing the HRIT signal [12][13]. The hardware digitizer designed for the prototype receiver is similar in nature to the USRP design, however unlike the USRP, the prototype hardware was not developed for direct commercial use. This device is referred to as the Aerospace Intermediate frequency Digitizer (AID).

Although not shown in Figure 1, ground systems require that the satellite dish be powered. The AID as designed for this prototype solution does not supply power to the satellite dish, therefore an alternate means of powering the dish is required. The LNB devices used by some ground systems may be unable to supply power to drive the AID board. An inline amplifier will be required in these situations.

#### 2.2 Hardware Overview

The AID is a mixed signal hardware board with components that are typical of any communication system. The general characteristics of the board are summarized in Table 2. The input signal power must be between -70 and -5 dBm. The hardware can process signals that have a baud-rate of 10 mega-symbols per second, with bandwidths as large as 20 MHz. However, the software components of the receiver limit the achievable system throughput to much lower values. The current board design is meant to handle downconverted-signals between 130 and 150 MHz. The cost of printing the board and purchasing all of the components is under US \$100. A summary of the major components is shown in Table 3.

<sup>&</sup>lt;sup>3</sup> LNA stands for Low-Noise Amplifier

Figure 1. EMWIN/HRIT system diagram.

Table 2. AID Specifications

| Part Cost                | Approximately \$100    |

|--------------------------|------------------------|

| Sensitivity              | -70 dBm to -5 dBm      |

| IF Range                 | 130-150 MHz            |

| Power                    | 1.5 Watts, USB Powered |

| Maximum Signal Bandwidth | Up to 20 MHz           |

| Maximum Signal Baud Rate | Up to 10 Msps          |

Table 3. AID List of Major Components

| Anti-Aliasing Filter           | 20 MHz Bandwidth, fc=140 MHz, |

|--------------------------------|-------------------------------|

| _                              | Insertion loss 11 dB          |

| AGC                            | Maximum Output (13 dBm)       |

| ADC ( Analog to Digital Conv.) | 64 Mega-samples /second       |

| FPGA                           | 5980 Logic Elements           |

| USB Controller                 | 24 MHz Input Clock            |

#### 2.2.1 AID Front End

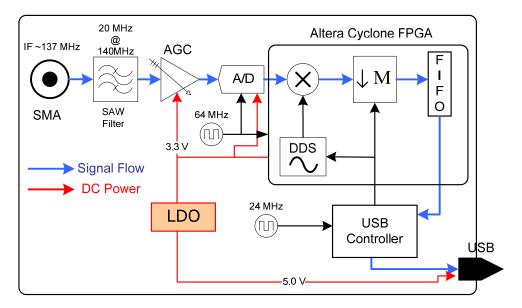

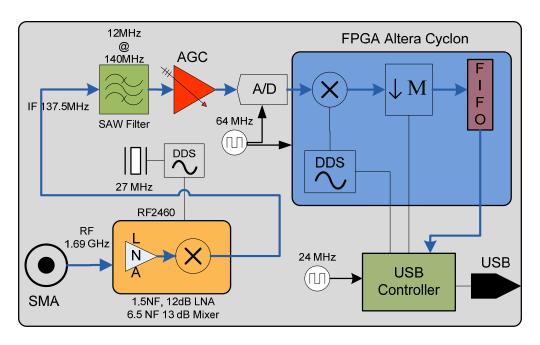

The front-end analog portion of the AID performs filtering and amplification, while the digital portion samples the analog waveform, down converts it from IF to baseband, and finally streams the digital samples to the computer via the USB controller. The data is sampled with the Analog-to-Digital Converter (ADC) while the down-conversion and down-sampling of the digital samples are performed by a Field Programmable Gate Array (FPGA).

The signal at the AID's SMA $^4$  input is assumed to have been received by a satellite dish down-converted from RF to IF in the range of  $140 \pm 6$  MHz. The input signal is also assumed to be DC blocked. The board was specifically designed to operate at 140 MHz to be compatible with legacy EMWIN solutions such as EMWIN-N and EMWIN-I.

To suppress out-of-band thermal noise and non-HRIT signals, a 20-MHz wide Surface Acoustic Wave (SAW) filter, with a center frequency of fc = 140 MHz, was used as a first element in the receiver chain. The bandwidth of the filter was chosen to be larger than the bandwidth of the signal to accommodate an array of different weather satellite signals. Typically, the large insertion loss (11 dB) introduced by the SAW filter would affect the overall power; however, the board was designed to receive a signal that has already been boosted. The only amplification capability on the board is the Automatic Gain Controller (AGC) that is driven by the output of the SAW filter. The output of the AGC goes to the ADC for conversion.

The ADC used in the design has 12-bit resolution and is sampled at 64 MHz<sup>5</sup>. Because the sampling frequency of the ADC is less than twice the bandwidth of the IF-signal, the hardware is performing IF-sampling (sub-sampling) instead of direct sampling. The principles of IF-sampling will be detailed further in Section 3.1.3.1.

Although the FPGA and ADC are efficient enough to down-convert a communication signal with very high baud rates, the USB device presents a communication bottleneck of 256 Mega bits per second (Mbps) for transferring output bits to a PC. This bottleneck restricts the maximum input signal baud rate to just over 10 Mega-symbols per second (Msps). Since the HRIT will have a symbol rate of less than 1 Msps, the USB interface provides sufficient throughput for this application.

#### 2.2.2 AID Power Meter

The AID has an LED power meter that indicates the power of the input signal as shown in Figure 2. The LED is driven by the output of the AGC. Below is a photo of the AID board, with enclosure and LED power meter. The power meter is intended to provide a visual aid for users while aligning the satellite dish to maximize signal strength.

-

<sup>&</sup>lt;sup>4</sup> SMA is a SubMinature version A connector

<sup>&</sup>lt;sup>5</sup> The original design of the AID box had an ADC running at 48 MHz.

Figure 2. LED example.

#### 2.2.3 Power Consumption

The AID can be powered completely by the USB port, requiring no additional AC power sources. The board takes in 5 Volts from USB port and uses 270mA, thus consuming under 1.5 Watts of power.

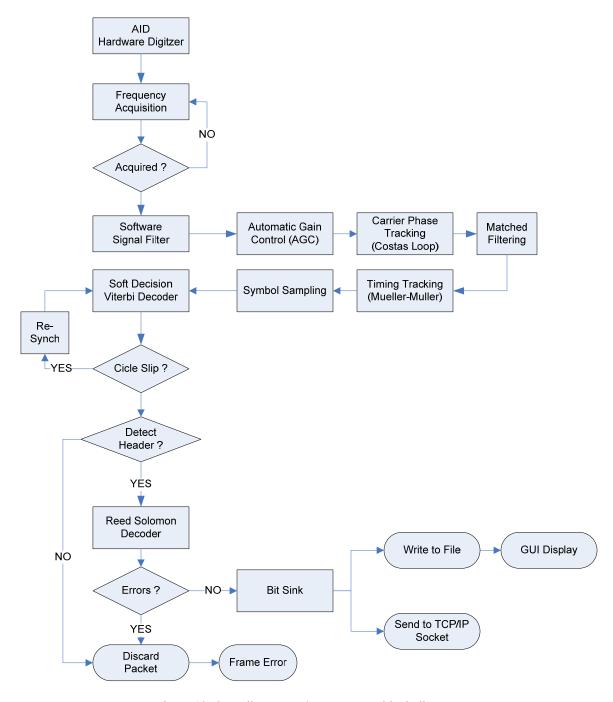

#### 2.3 Software Overview

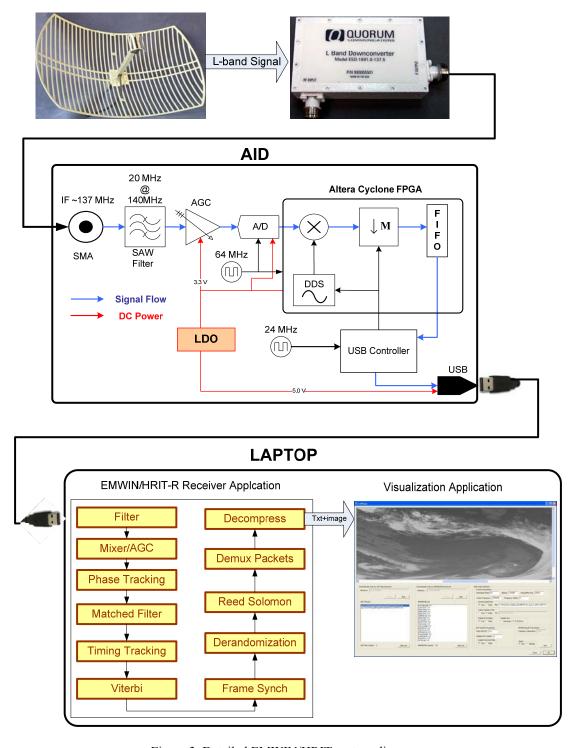

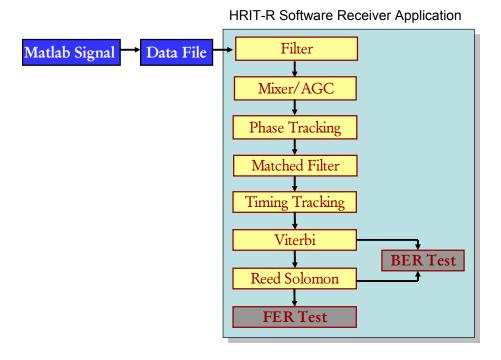

The EMWIN/HRIT software radio continuously grabs data off of the USB port and demodulates it in real time. As stated earlier, most of the signal processing is done in software, maximizing flexibility and minimizing the amount of additional hardware necessary to process the desired signals. A simplified block diagram of the software is shown in the bottom portion of Figure 3. Although not shown, the first operation by the software is to acquire the carrier frequency. The operation only happens occasionally, thus the first persistent processing block of the software radio is a filter to isolate the exact signal of interest and reject all other signals. After that, the software performs the core functions of digital demodulation: phase tracking, matched filtering, and timing tracking. In the case of EMWIN-N, LRIT, and HRIT, the tracked digital data is sent to a Viterbi decoder for decoding. After that, the data has finally been converted from an IF analog signal, at the output of the LNB, into binary data. From there, additional processing, like Reed-Solomon (RS) decoding, is done to convert the bit-stream into text and images to be viewed using a visualization graphical user interface (GUI).

Table 4 summarizes the EMWIN/HRIT software. The software requires a computer system equipped with a dual-core Intel Processor with Streaming SIMD Extensions version 3 (SSE3)<sup>6</sup> and approximately 1 GB of RAM. The computer also needs at least one free USB 2.0 port. The software was built around multiple libraries including: GNU Radio 3.1.2, the FFTW library "Fastest Fourier Transform in the West", Intel Performance Primitives, and USB libraries. These libraries are of interest to designers, but are completely irrelevant to the end-user. The software currently achieves a maximum speed of over 1.5 Msps, resulting in plenty of computer processing margin.

\_

<sup>&</sup>lt;sup>6</sup> In 2009, all dual-core Intel processors had SSE3 extensions.

Figure 3. Detailed EMWIN/HRIT system diagram.

Table 4. Software Specifications

| Operating System              | Windows XP                     |

|-------------------------------|--------------------------------|

| Interface                     | USB 2.0                        |

| Max Throughput (as of today ) | 1.5 Msps                       |

| EMWIN/HRIT Requirements       | Intel Dual Core Processor. 1GB |

| _                             | RAM                            |

| Software Libraries Used       | GNU Radio 3.1.2, FFTW, Win-    |

|                               | libUSB32, Intel Performance    |

|                               | Primitives                     |

# 3. Hardware Description and Performance

# 3.1 Hardware Design

Section 2.2 provided a brief overview of the AID hardware board. This section will go into much greater detail about the hardware board. For a detailed description of how the hardware interfaces with the software, and a detailed look at the schematics, please see Section Appendix B.

For convenience, the AID diagram is shown in Figure 4, where three distinct circuits are highlighted: clock, signal, and power.

Figure 4. AID diagram.

#### 3.1.1 AID: Power Circuit

The AGC, ADC, and FPGA all operate at 3.3 V, while the USB device runs at 5V. A Low-dropout regulator (LDO) is used to produce two voltage levels across the board.

#### 3.1.2 AID: Clocking Circuit

A 64 MHz crystal is currently used to drive the FPGA and the ADC, while a 24 MHz crystal is used to drive the USB controller.

#### 3.1.3 AID: Signal Circuit

The signal line starts at the SMA connector input and ends at the USB output connector. The signal path represents a typical flow for A/D sampling. The following subsections will analyze in detail the methods used for digitizing and processing the received signals.

## 3.1.3.1 AID: IF Sub-sampling

The new HRIT signal will have a baud rate of less than 1 Msps, resulting in a Nyquist sampling rate of 2 Mega-samples/second (Msamps/s). If the signal was sampled at baseband, we would only need an ADC operating at above 2 MHz. As shown in Figure 4, the AID samples directly at IF (~140 MHz), instead of shifting the signal down to baseband first. This form of sampling is referred

to direct IF-sampling, or sub-sampling, since the ADC sampling frequency is less than twice the highest frequency (280 MHz).

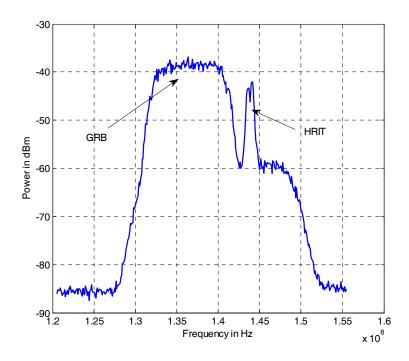

The bandwidth of interest spans from 134 to 146 MHz, which results in a Nyquist rate of 24 Msamps/s The reason the bandwidth of interest is so large is because signals of interest for GOES-R users might be at several distinct IF frequencies across the frequency span. The input bandwidth is restricted by the SAW bandpass filter (BPF). The exact frequency response of the filter is shown in Figure 5.

Figure 5. SAW filter frequency response.

Sub-sampling uses the general principle of sampling theory [14]. Figure 6 shows a block diagram of the signal processing done by the AID board. The first block is the SAW BPF, followed by signal processing blocks implemented by the FPGA, which include: the mixer, the decimator, and the low-pass filter. The AGC has no implicit role in sub-sampling and is thus omitted from the figure.

Figure 6. IF-Sampling block diagram.

There are two signals of interest shown in Figure 6, the output of the BPF and the output of the ADC. To illustrate the theory behind IF-sampling, the following example illustrates how sub-sampling works for two signals in our band of interest.

# Example: Sub-sampling

Let the input signal be a real waveform with a bandwidth of 400 kHz and a center frequency of 137.5 MHz (these are actually similar characteristics to the LRIT signal). Figure 7 shows the spectrum of Signal-1. The full spectral representation shows spectral content at ±137.5 MHz. The positive spectral image is colored **red**, while the negative content is colored **gray**. The SAW-filter filters this spectrum such that the bandwidth of the signal being sampled does not exceed 20 MHz. In this example, the signal is much less than 20 MHz so the input and output of the BPF are equivalent.

The spectrum of the sampled waveform, Signal-2, is shown in Figure 8. This spectrum follows the standard laws of sampling. Copies of the "negative" and "positive" peaks are spaced every 64 MHz, which is the assumed sampling frequency. The negative copies of the spectrum have aliases at {..., -137.5, -73.5, -9.5, 54.5, 118.5, 182.5, ...} MHz, while the positive copies fall at {..., 137.5, 73.5, 9.5, -54.5, -118.5, -182.5,...} MHz. The figure shows that the negative and positive images are separated by 19 MHz, thus there is no aliasing between the negative and positive images, despite the fact that the signal was not sampled at the direct Nyquist rate of 280 MHz.

As illustrated in Figure 8, the closest signals to baseband are images centered around 9.5 MHz. The mixer, shown in Figure 6, with frequency Fc = 9.5 MHz, brings the images down to baseband. If the IF frequency of interest, f, is between 136 and 144 MHz, the mixer frequency needs to be set to Fc = f - 2\*64 MHz, to bring the IF signal to baseband.

Figure 7. IF Sampling Signal 1.

Figure 8. IF Sampling Signal 2.

# 3.1.3.2 Choosing the Sampling Frequency for the AID

The USB controller has the capability of producing a 48 MHz clock output by multiplying a local 24 MHz reference clock by a factor of two, and by using a phase-locked loop. When the AID box was originally designed, in order to minimize component costs, the same 48-MHz signal was initially used to control the ADC.

The sampling approach described in the example above worked great for EMWIN/LRIT legacy signals, running either at 48 or 64MHz. However, the final GOES-R frequency plan, with the HRIT signal at 1697.4 MHz generated some aliasing problems when using a 48-MHz clock.

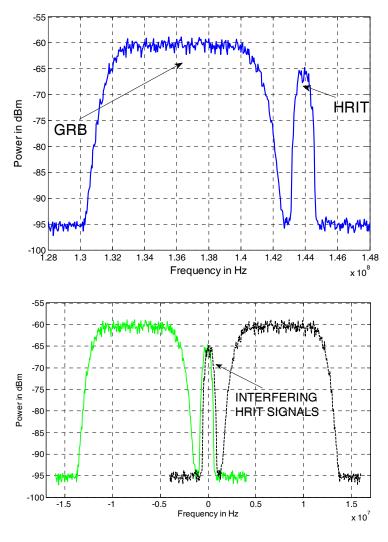

On Figure 9, we show a plot of the spectrum for the GOES-R signals Global Re-Broadcast signal (GRB) and HRIT after converting from L-band to an IF frequency. The GRB signal is centered at 136.5 MHz and is 12-MHz wide, while HRIT is centered around 143.9 MHz and is around 1.35-MHz wide. When this signal is sampled at 48 MHz with the approach described above, the HRIT images will interfere with each other causing a significant degradation on the overall performance.

Figure 9. Spectrum of GOES-R image using 48 MHz sampling. The HRIT signals are interfering.

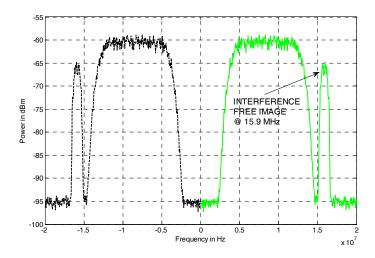

Figure 10. Spectrum of GOES-R image using 64 MHz sampling. The HRIT signals are not interfering.

The GOES-R signals do not interfere when driving the ADC with a 64 MHz clock. This was done by simply replacing the clock that feeds the ADC on the AID board. The current FPGA firmware design and software accommodates a 64 MHz clock, so no changes were needed when changing the ADC clock to 64 MHz. In general, arbitrarily changing the ADC clock will require simple changes to the FPGA firmware design and software.

## 3.1.3.3 AID: Filtering and Decimation

In traditional digital communication systems, the only step left after sampling a signal would be to digitally low-pass filter (LPF) the baseband signal and send the digital data out for further processing. Because we are performing IF-sampling, there is one additional step to consider before sending the data out, and that is decimation.

Without decimation, the output digital signal would have a rate of 64 Msamps/s and with an ADC resolution of 12 bits, the resultant USB output sample rate would be 576 Msamps/s. Streaming 576 Msamps/s over a USB interface is not possible. Even if the USB interface could sustain that data rate, the software demodulator would not be able to keep up (using a typical consumer grade PC). The purpose of decimation is to reduce the data rate as much as possible before sending it to the PC.

In general, let R be the symbol rate of the signal under study. Let *Fs* be the sampling frequency of the ADC, and M be the decimation rate as shown Figure 6. The number of samples per symbol is simply Fs/R/M.

For the AID device, Fs is fixed at  $64x10^6$ . The symbol rate of the signal of interest is usually known, so the decimation rate can be chosen accordingly to achieve a desired number of samples/symbol. A demodulator should have at least 2 samples/symbol to be able to correctly recover the transmitted signal. At the same time, processing a higher number of samples per symbol reduces the overall throughput, measured in symbols per second (sps). If decoding speed is not a critical issue, as a rule of thumb for a BPSK transmission, we set the samples/symbol to four. When trying to maximize the possible throughput, we set the samples/symbol to two.

The HRIT software demodulator can work with any number of samples/symbol greater than two, but there is no reason to overburden the software with more samples per symbol if it won't increase the

quality of the received data. The samples/symbol must be as close to an integer value as possible in order for the software to work properly.

The decimation range of the AID is any even integer between 2 and 256. When demodulating the LRIT or EMWIN/HRIT signal, the software chooses a decimation rate that results in 2 samples/symbol by default.

The following example illustrates how decimation works. Let the input signal be 293,883 sps. Without down-sampling, there would be  $64 \times 10^6 / 293,883 = 217.78$  samples/symbol. Decimating by 108 would result in 2.01 samples per symbol, and is the default decimation rate used by the prototype receiver to digitize the current LRIT signal. Table 5 shows the parameters for receiving LRIT, EMWIN-N, and EMWIN-I.

Table 5. EMWIN/LRIT Configuration

| Product                            | HRT       | LRIT       | EMW IN     | EMW IN            |

|------------------------------------|-----------|------------|------------|-------------------|

| M odulation                        | BPSK      | BPSK       | OQPSK      | FSK               |

| RF Frequency [MHz]                 | 1697.4    | 1691       | 1692.7     | 1690 <i>.</i> 725 |

| IF Frequency [M H z]               | 143.9     | 137.5      | 139.2      | 137.225           |

| Data Rate (R ) [sps]               | 927,000   | 293,883    | 17,970     | 9,600             |

| ADC Sampling Frequency (Fs) [MHz]  | 64        | 64         | 64         | 64                |

| MixerFrequency(Fc)[MHz]            | 15.9      | 9.5        | 11.2       | 9.225             |

| Decim .Rate (M ) / SamplesperSymb. | 1 / 69.04 | 1 / 217.77 | 1 / 3561.5 | 1 / 6666.6        |

|                                    | 16 / 4.3  | 54 / 4.03  | 88 / 40.47 | 74 / 90.09        |

|                                    | 22 / 3.13 | 72 / 3.02  | 178 / 20   | 98 / 68.02        |

|                                    | 34 / 2.04 | 108 / 2.01 | 222 / 16   | 136 / 49.01       |

Now that the principles of sub-sampling have been covered, the real FPGA implementation will be treated.

# 3.1.3.4 Implementation of a Digital Down-Converter on an FPGA

The FPGA digital down converter is shown in Figure 11.

# $g\left(i \stackrel{t}{/}_{T_s}\right) = g_I(t)\cos\left(i \cdot \omega_c \stackrel{t}{/}_{T_s}\right) - g_Q\sin\left(i \cdot \omega_c \stackrel{t}{/}_{T_s}\right), \text{ SSB signal}$ $g\left(i \stackrel{t}{/}_{T_s}\right) = g_I(t)\cos\left(i \cdot \omega_c \stackrel{t}{/}_{T_s}\right) - g_Q\sin\left(i \cdot \omega_c \stackrel{t}{/}_{T_s}\right), \text{ SSB signal}$ $2\cos\left(i \cdot \omega_c \stackrel{t}{/}_{T_s}\right) \qquad \qquad \downarrow 2$ $2\cos\left(i \cdot \omega_c \stackrel{t}{/}_{T_s}\right) \qquad \downarrow 2$ $g_Q\left(M \cdot i \cdot \stackrel{t}{/}_{T_s}\right) \qquad \downarrow 2$

Figure 11. FPGA digital down-converter implementation.

Recall that the mixer, down-sampling and low-pass filtering are all implemented on the FPGA chip on the AID. The user can control the mixer frequency,  $f_c$ , and the decimation rate M. The low pass filter coefficients are automatically computed given the user choice of M, such that the cutoff frequency is  $(64 \times 10^6 / \text{M/2})$ .

The mixer is implemented via the CORDIC algorithm which multiplies incoming IF waveforms by a complex valued exponential [15]. Decimation, which includes down-sampling (dropping samples) and filtering, are done together in practical digital systems. One of the more efficient low-pass and down-sampling filtering algorithms is the Cascaded Integrator Comb (CIC) filter [16] which is implemented on the AID board. Lastly, there is a First-Input-First-Output (FIFO) buffer between the USB controller and FPGA to manage the data transfer. The FIFO depth is not programmable by the user.

The FGPA code was designed to operate in multichannel mode with two transmit and two receive channels. The AID only needed to operate one receive channel. This allowed us to implement a single channel version of the original FGPA code. Our single channel design is much smaller, and fits on an FPGA that is cheaper and consumes less power than the original FPGA. The FPGA used is a Cyclone EP1C6, which contains 5980 logical elements.

#### 3.2 Hardware Performance

There are number of factors that influence the performance of the device, e.g., the sampling frequency of the ADC, the noise figure of the system, the noise introduced into the system due to clock jitter, the anti-aliasing filter, and other aspects. The best measure of board performance is the overall *noise figure*. The noise figure of the AID was estimated to be around 18 dB. The single best way to improve performance would be to get a better clock to drive the FPGA and ADC, however, the clock that was chosen was adequate to meet system specifications.

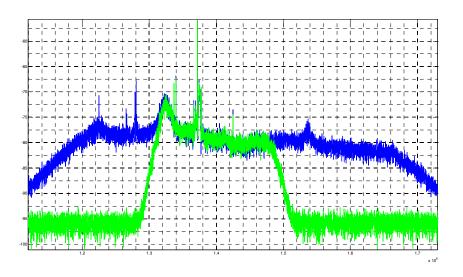

In order to characterize the performance of our IF-sampler, we measured the amount of folded noise in the band of interest that occurred as a result of sampling. To conduct this experiment, a live signal from GOES-12 was used. Figure 12 illustrates a plot of the captured signal. The blue line shows the frequency response of the LNB, which has a bandwidth of 50 MHz, while the green line shows the frequency response of the signal after being filtered with a SAW filter. The performance degradation due to folding was minimal.

Figure 12. Spectrum of live GOES-12 signal.

# 4. Software Description

In this section, we describe the signal processing blocks designed to demodulate LRIT, EMWIN-I, and EMWIN-N. Throughout this section, we will reference the different file names of the source code used to implement the different processing blocks. For example, when a finite impulse response (FIR) filter-block is shown, it will referred to as  $gr\_fir\_filter$ , because that block is implemented using the file  $gr\_fir\_filter.cpp$ .

We begin this section by describing the general software framework used to design the EMWIN/HRIT software receiver in Section 4.1. We then describe in Section 4.2, a carrier acquisition algorithm that is performed before demodulating any communication signal After that we investigate the LRIT transmission specification and the LRIT software receiver architecture in Sections 4.3 and 4.4, respectively. The EMWIN-N and EMWIN-I are likewise treated in the subsequent sections. A brief description of the Soft-decision Viterbi decoder appears in Section 4.7.

#### 4.1 Software Framework

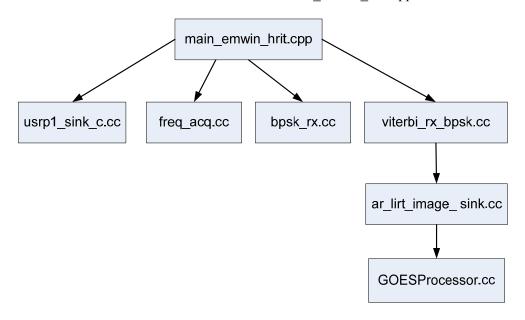

As stated earlier, the software was developed with a free open source software development suite called GNU Radio [8]. The GNU Radio framework provides an environment that allows a simple interconnection of different C-written subroutines. The GNU Radio paradigm allows different programmers to write custom digital-communication blocks that can be easily configured and connected using basic C++ syntax. Once all the blocks are configured and connected, GNU Radio automatically streams data from beginning to end without the need for explicit user control. The user-controlled initial state of the software blocks can be found on Table 6.

The environment of connecting the blocks and streaming data in GNU Radio is resource-efficient, making GNU Radio a good framework for designing real-world radio applications. The main bottlenecks in GNU Radio come from the implementation of the actual communication blocks, for example, filtering, error correcting decoding, etc. In order to take advantage of the powerful GNU Radio framework but also produce an application with high performance, it is best for users to write their own communication blocks, or simply optimize the blocks that already exist in the GNU Radio library. In order to develop the EMWIN/HRIT solution, several GNU Radio-blocks were optimized and many new blocks were created in order to build a system that works according to the specifications. In many cases, blocks were written using the Intel® Performance Suite 5.1 [17]. This library allows many mathematical operations to be performed in parallel, using specific low-level Intel-processor instructions. Vector multiplications and matrix operations can be efficiently pipelined in order to increase the overall system throughput. The system diagram in Figure 13 shows the logic behind the software radio components of the EMWIN/HRIT solution. Each of the software-blocks that are part of this solution are described in the following sections.

Figure 13. Overall EMWIN/HRIT system block diagram.

Table 6. AID User-Defined Input Parameters

| Parameter                                   | Comm<br>and<br>Flag                          | Default Value                                                                                                                                           | Description                                                                                                                                                                                                     |

|---------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable File Sink -wr 0                      |                                              | Write raw USB samples directly to disk. Output file will be located in c:\temp\usrp_log\                                                                |                                                                                                                                                                                                                 |

| Decimation Rate                             | -dr                                          | Depends on<br>Signal range:<br>[2-256]                                                                                                                  | Sets the decimation rate on the FPGA.<br>See Table 5                                                                                                                                                            |

| Center IF-Frequency                         | -fc                                          |                                                                                                                                                         | For the LRIT Signal, default values is 137.5 MHZ, for EMWIN-I, 137.225 MHz, and for EMWIN-N is 137.9 MHz. 143.9 MHz for HRIT                                                                                    |

| Enable Software Filter                      | -Ifilter                                     | 1                                                                                                                                                       | Enable software rejection filter                                                                                                                                                                                |

| Repeat Incoming<br>Waveform                 | -repeat                                      | 0                                                                                                                                                       | If the radio is run using a recorded user-<br>file, this flag enables the receiver to repeat<br>the incoming waveform once it reaches<br>the end of file This is a useful feature for<br>bit error rate testing |

| Roll off Factor                             | -roll                                        | 0.5<br>Range: [.19]                                                                                                                                     | Roll-off factor for square root-raised cosine pulse shaping                                                                                                                                                     |

| Bit Rate                                    | -br                                          | Depends on<br>Signal                                                                                                                                    | 293,883 for LRIT, 17970 for EMWIN-N, 9600 for EMWIN-I, 927,000 for HRIT.                                                                                                                                        |

| Buffer Size                                 | -buff                                        | 64 [kbytes]                                                                                                                                             | For multi-threaded applications, this parameter defines the size of the buffer between threads                                                                                                                  |

| Use Recorded Data?                          | -rec                                         | 0                                                                                                                                                       | Allows software radio to run reading a pre-<br>recorded file stored on a network drive<br>instead of using data from the USB port of<br>the AID box.                                                            |

| Timing Bandwidth                            | ming Bandwidth -tbw 3000[LRIT] 1000[EMWIN-N] |                                                                                                                                                         | Indicates the factor that divides the symbol rate of the desired signal to determine the timing-loop bandwidth for LRIT or HRIT and EMWIN-N only                                                                |

| Phase Bandwidth -pbw 100[LRIT] 200[EMWIN-N] |                                              | Indicates the factor that divides the symbol rate of the desired signal to determine the phased-locked-loop bandwidth for LRIT or HRIT and EMWIN-N only |                                                                                                                                                                                                                 |

# 4.2 Frequency Acquisition

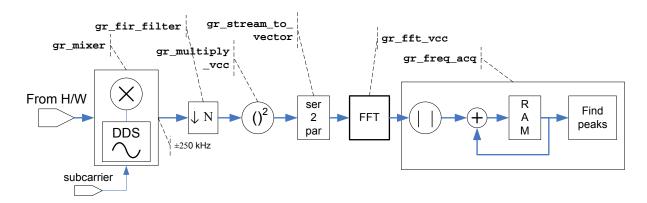

The purpose of the block is to estimate the center frequency of a sampled communication waveform. The constituent blocks of the acquisition engine are shown in Figure 14. The core of this software engine is based on averaging the successive Fast Fourier Transforms (FFT) of the incoming signal. The frequency-search window (that depends on the initial frequency uncertainty), the bin-resolution, and the amount of bin-averaging are all runtime programmable. The command-line frequency acquisition options and default values are described in Table 7. A fourth-law detector has been provided to lock onto the BPSK subcarrier. For the offset quadrature phase-shift keying (OQPSK) case a square-power detector is used. The search window size and bin resolution values determine the FFT size.

Figure 14. Block diagram of software-based frequency acquisition.

Table 7. Configuration for Frequency-Acquisition Subroutine

| Parameter                  | Command<br>Flag | Default<br>Value | Description                                                                                                                                                                 |

|----------------------------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable / Disable           |                 |                  | •                                                                                                                                                                           |

| Freq.Acq                   | -acq            | 1                | Frequency acquisition is enabled by default.                                                                                                                                |

| Bin resolution             | -fa_res         | 50 Hz            | Frequency bin-resolution                                                                                                                                                    |

| Freq. Range                | -fa_range       | 50 kHz           | Initial frequency uncertainty to search for                                                                                                                                 |

| Detection Rule             |                 |                  |                                                                                                                                                                             |

| Square-Law                 | -fa_2           | 0 or 1           | Depends on signal of interest and SNR. Default method for OQPSK.                                                                                                            |

| 4th order Law              | -fa_4           | 0 or 1           | Depends on signal of interest and SNR. Default method for BPSK.                                                                                                             |

| Absolute Power             |                 |                  | f Square and 4th Power are disabled, then this method is enabled. Used in some low SNR scenarios. Default for FSK.                                                          |

| FFT Averages               | -fa_numfft      | 16               | Number of times FFT algorithm is run to measure the frequency content of a specific bin                                                                                     |

| Forced Frequency<br>Offset | -foff           | 0                | User can set a desired frequency offset that adds to the value that the frequency algorithm obtains. Or one can turn acquisition off, and enter in a known offset manually. |

A peak-search algorithm is run once the desired number of averaged FFTs have been computed. The acquisition engine will return a set of bins whose integration-value determine the likelihood of the signal of interest having frequency contents on that particular bin. Each detected peak will therefore have an associated power metric. Let  $\vec{P_0}(N)$  be the length-N vector of measured power levels. The acquisition engine creates a vector of sorted metrics  $\vec{P_s}(N)$  where, without loss of generality, we assume that  $P_s(0) \le P_s(1) \le \cdots \le P_s(N)$ . The peak-frequency is determined by computing the center of mass for the largest bin and the adjacent eight bins. Let  $P_0(Max)$  be the bin in the unsorted power metric vector that is mapped to the sorted metric  $P_s(N)$ . The power metric can then be defined as:

$$P_{m} = \frac{\sum_{i=-4}^{4} P_{0} (Max - i)}{\frac{4}{N} \sum_{i=0}^{N/4} P_{s}(i)}$$

The denominator can be thought of as the noise power, while the numerator is the signal power. Recall that when a BPSK signal of the form  $\pm Ae^{j\omega_c t}$  is sent through a square-law detector, the output is ideally an impulse function. This implies that in order to measure the signal power one would ideally require summing over only a single bin on the numerator. However, due to the imperfect size of the FFT-bins, our experiments show that considering eight adjacent bins is a better indicator of the true signal level. At low SNRs, squaring or quadrupling the value of a particular bin can have severe squaring-losses. Therefore the SNR operating point must be considered before choosing a specific frequency-acquisition method.

# 4.3 LRIT Transmitter Specifications

The digital LRIT is an international standard for data transmission that was developed by the Coordination Group for Meteorological Satellites (CGMS) in response to the recommendation for digital meteorological satellite broadcasts. The CGMS Global Specification provides the standard that is supported by all operational geostationary meteorological satellites to be flown by the United States, European agencies, Japan, China, and Russia. The NOAA and other world meteorological agencies have developed subsequent system specifications, designs, and implementations of their specific LRIT systems. The origin of the name LRIT is due to its initial low data rate of 293 ksps.

The full LRIT specification can be found at [5][6]. The packetization process of LRIT data follows a standard developed by the Consultative Committee on Space Data Systems (CCSDS). Below is a summary of steps for converting image data into an LRIT waveform.

#### 4.3.1 LRIT Transmission Process

- Compress image data with Rice coding [18]

- Add CRC (Cyclic Redundancy Check)

- Create Virtual Channel Data Unit (VCDU) data payload out of compressed image data

- Assemble Coded Virtual Channel Data Unit (CVCDU) packet

- o Reed Solomon encode VCDU data payload

- o Add VCDU deader

- Assemble the Channel Access Data Unit (CADU) packet

- o Randomize CVCDU packet

- Add synchronization header

- Viterbi encode CADU packets continuously without termination

- Modulate Viterbi encoded data using BPSK modulation

For a more detailed description of the transmission process, please see the specification. [5][6]. In Table 8, key LRIT signal parameters are presented.

Table 8. Key LRIT Transmission Parameters

| Parameter                | Value                                                           |  |  |

|--------------------------|-----------------------------------------------------------------|--|--|

| Satellite Service        | GOES-11 (West), GOES-12 (East), GOES-13, GOES-14                |  |  |

| Modulation               | BPSK                                                            |  |  |

| Center Frequency         | 1691 MHz                                                        |  |  |

| Typical (140 MHz) IF     | 137.5 MHz                                                       |  |  |

| Frequency                |                                                                 |  |  |

| Measured Symbol Rate     | 293,883 symbols/second                                          |  |  |

| Pulse Shape              | Root Raised Cosine (α= 0.5)                                     |  |  |

| Forward Error Correction | <ul> <li>Type: Convolutional (Soft-Decision Decoder)</li> </ul> |  |  |

| Encoder                  | Rate: ½                                                         |  |  |

|                          | <ul><li>Constraint Length: 7 bits</li></ul>                     |  |  |

|                          | ■ Generator:                                                    |  |  |

|                          | G1 = 1111001; G2 = 1011011                                      |  |  |

|                          | Symbol Inversion: none                                          |  |  |

|                          | ■ Puncturing: none                                              |  |  |

| Synchronization Header   | 1ACFFC1D                                                        |  |  |

| Randomizer Polynomial    | $h(x) = 1 + x^3 + x^5 + x^7 + x^8$                              |  |  |

| Reed Solomon             | (255, 223) code symbol interleaving I = 4                       |  |  |

| CRC Check Polynomial     | $g(x) = 1 + x^5 + x^{12} + x^{16}$                              |  |  |

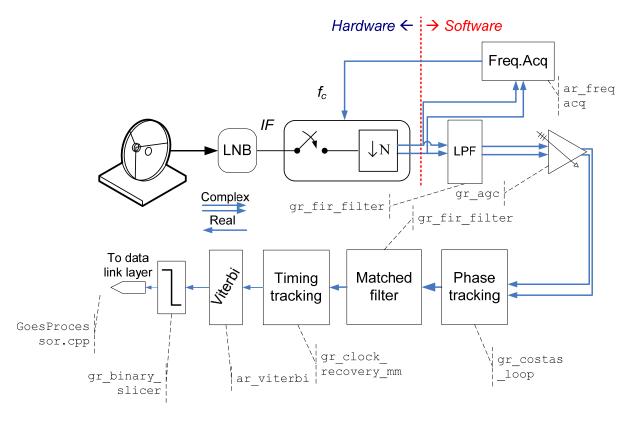

#### 4.4 LRIT Software Receiver Architecture

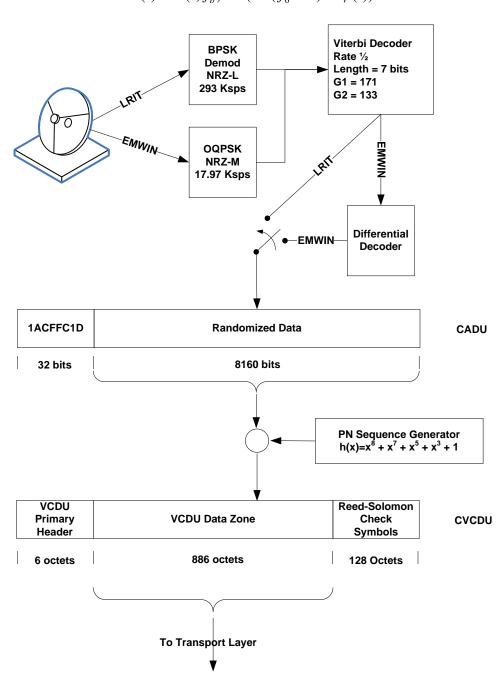

The steps required to process an LRIT file from the transmitted data are shown in Figure 15. As stated earlier, the first step to demodulate LRIT is carrier acquisition. After carrier acquisition, the signal is low-pass filtered to reject all adjacent signals. The signal rejection filter can be turned on and off using the flag specified in Table 6. After bringing the signal down to baseband and filtering out interference, phase tracking, matched filtering, timing recovery, and convolution decoding via the Viterbi algorithm are performed. The data link layer takes the output of the Viterbi decoder consisting of blocks of 8160 bits, with each block being preceded by a 32 bit header for synchronization. These 8160 data bits have been randomized to assure sufficient bit transitions using the polynomial  $h(x) = 1 + x^3 + x^5 + x^7 + x^8$ . The de-randomized bits form a Coded Virtual Channel Data Unit (CVCDU) as shown in Figure 15. The first 892 octets of the 1020 octets in the CVCDU correspond to the header and data bits of a systematic (255,223) RS code [20]. By using a systematic code, the 892 octets are not modified by the RS channel code. This implies that under high SNR values the VCDU data could be used without RS decoding. The network layer forwards the RS decoded packets to the transport layer that takes care of reassembling the LRIT files that were subdivided before transmission. The session layer is next, where the CRC field checks for packet integrity using the polynomial  $g(x) = 1 + x^5 + x^{12} + x^{16}$ . The presentation layer will finally convert the decompressed LRIT files into user data files. The type of files that will be received include: image data files, service messages, alphanumeric files and Global Telecommunication System (GTS) messages.

The BPSK signal of interest is defined by the bit rate,  $f_{\it b}$  , and the subcarrier frequency,  $f_{\it c}$ :

$$X(t) = m(t, f_b) \cos(2\pi (f_c + \Delta + f_0)t + \phi(t))$$

where  $f_0$  is a frequency offset introduced by the channel,  $\Delta$  is the difference between the transmitter and receiver frequencies,  $\phi(t)$  is a phase offset and  $m(t, f_b)$  is the information message to be recovered. A conventional BPSK demodulator circuit with separate phase and symbol tracking loops is used for demodulation, as shown in Figure 16. The signal at the input of the software radio has

already been frequency-shifted from  $f_c$  to baseband and decimated in the digitizer to reduce the computational requirements:

$Y(t) = m(t, f_b) \cos(2\pi (f_0 + \Delta)t + \varphi(t))$

Figure 15. The LRIT and EMWIN-OQPSK packet structure.

An optional software-decimator can be added to further reduce the bit rate. For this particular implementation, we only use the decimator at the digitizer and use the data rates shown in Table 5. An additional low-pass software filtering stage is added to the input of the radio to remove undesired neighbor frequency contents.

The LNB from the hardware interface translates the incoming frequency of the LRIT signal, from 1691 MHz down to  $f_c=137.5$  MHz. However, due to the sub-sampling method used, the effective center frequency is  $f_c'=9.5$  MHz, giving  $\Delta_{\rm max}=(9.5\times10^6)(200\times10^{-6})=1.9$  kHz, assuming a 200 ppm frequency tolerance on both the transmitter and receiver oscillator references. Phase tracking by means of a Costas loop [19], can be applied to remove the dynamic frequency offset,  $f_0$ , introduced by the channel and the offset due to unmatched reference clocks. Following this stage, a filter matched to the root raised cosine pulse shape is used for maximizing the SNR in the presence of additive stochastic noise. A Mueller-Müller timing error detector [26] is used to recover the symbol timing of the signal.

Once the timing properties of the signal have been recovered, a convolutional Viterbi decoder is used for error correction. Building a software Viterbi decoder that was able to handle the projected data rates of 900 ksps was one of the greatest challenges in this project. Since one of the ideas of GNU Radio is to be able to reuse signal processing blocks, we chose to build a flexible decoder that could handle any constraint length, rate and polynomial choice. Since the full specifications of the future GOES broadcast signal are not completely defined, we decided that the practical advantages of having a flexible decoder were better than designing a specific decoder for a particular channel code rate that could perhaps attain a higher throughput. Our initial design was able to maintain a throughput of around 300 ksps. Since this was not sufficient to handle the desi red rates, we carefully vectorized the algorithm using Intel IPP functions [17]. This redesign allowed us to increase our throughput to 1.89 Mbps when running the decoder on a dual processor Intel Xeon CPU at 3.7 GHz. In Figure 16, the signal flow in the receiver is shown, together with the name of GNU Radio blocks that are used in the implementation. Note that, for the case of the Viterbi decoder, the block has been labeled ar viterbi to indicate that this block was never a member of the GNU Radio library. The remaining blocks use the prefix gr, to indicate that they have been derived from the original GNU Radio library. This does not imply that these blocks remain unchanged from their original versions. In fact, all of them have been optimized using the Intel IPP libraries to enhance their throughput. The final signal-processing stage is a threshold slicer that generates output bits that are fed to the data link layer for image extraction.

Figure 16. Block diagram showing the different signal processing blocks in an LRIT BPSK receiver.

Table 9. Soft Decision Viterbi Decoding Parameters

| Parameter           | Command<br>Flag | Default<br>Value | Description                                                                                                                                                                    |

|---------------------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Minimum Threshold   | -vthresh        | 0.1              | Minimum bit error rate at the output of the Viterbi block, to declare that the decoder has solved its phase ambiguity                                                          |

| Test for Cycle Slip | -vperiod        | 10               | Indicates number of blocks before the Viterbi subroutine verifies that it is locked to the correct phase. For BPSK there are 2 possible states only. For OQPSK there are four. |

# 4.5 EMWIN-N Transmission Specifications

The full EMWIN specification can be found at [3][4]. Below is a summary of steps for converting EMWIN products into an EMWIN waveform.

#### 4.5.1 EMWIN-N Transmission Process

- Generate gif, jpg, zip, and txt products

- Create VCDU data payload out of EMWIN products

- Assemble CVCDU packet

- o Reed Solomon encode VCDU data payload

- Add VCDU header

- Assemble CADU packet

- o Randomize CVCDU packet

- Add synchronization header

- Viterbi encode CADU packets continuously without termination

- Apply binary differential encoding on the Viterbi encoded data

- Modulation data using Offset Quadrature Phase Shift Keying (O-QPSK)

Table 10 summarizes the key EMWIN-N signal parameters.

Table 10. EMWIN-N Key Parameters

| Parameter                | Value                                       |  |  |

|--------------------------|---------------------------------------------|--|--|

| Satellite Services       | GOES-13, GOES-14                            |  |  |

| Modulation               | OQPSK                                       |  |  |

| Center Frequency         | 1692.7 MHz                                  |  |  |

| Typical (140 MHz) IF     | 139.2 MHz                                   |  |  |

| Frequency                |                                             |  |  |

| Measured Symbol Rate     | 17970 symbols/second                        |  |  |

| Pulse Shape              | Root Raised Cosine (□= 0.5)                 |  |  |

| Forward Error Correction | Type: Convolutional (Soft-Decision Decoder) |  |  |

| Encoder                  | Rate: ½                                     |  |  |

|                          | Constraint Length: 7 bits                   |  |  |

|                          | Generator:                                  |  |  |

|                          | G1 = 1111001; G2 = 1011011                  |  |  |

|                          | Symbol Inversion: none                      |  |  |

|                          | Puncturing: none                            |  |  |

| Binary Encoding          | Differential Encoding                       |  |  |

| Synchronization Header   | 1ACFFC1D                                    |  |  |

| Randomizer Polynomial    | $h(x) = 1 + x^3 + x^5 + x^7 + x^8$          |  |  |

| Reed Solomon             | (255, 223) code symbol interleaving I = 4   |  |  |

#### 4.6 EMWIN-N Software Receiver Architecture

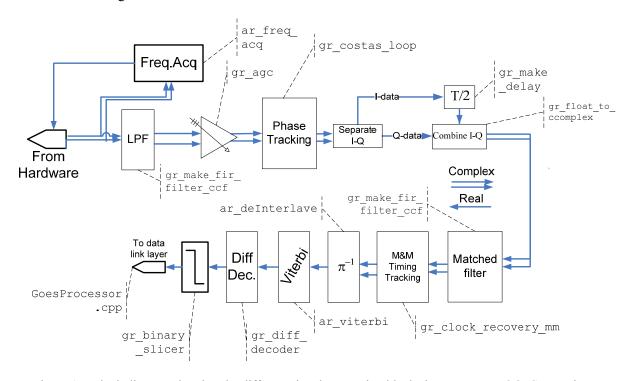

The EMWIN software receiver described herein was developed to satisfy GOES-N broadcast requirements. The user data format is shown in Figure 15. OQPSK modulation is a variant of phase-shift keying modulation using four different values of the phase to transmit information across a channel [19][21]. Taking four values of the phase (two bits) at a time to construct a QPSK symbol can allow the phase of the signal to jump by as much as  $180^{\circ}$  at a time. When the signal is low-pass filtered (as is typical in a transmitter), these phase-shifts result in large amplitude fluctuations which has an undesirable effect in communication systems. By offsetting the timing of the odd and even bits by half a symbol-period, T/2, the in-phase and quadrature components will never change at the same time. This will limit the phase-shift to no more than  $90^{\circ}$  at a time which yields much lower amplitude fluctuations than non-offset QPSK. The demodulation chain is shown in Figure 17.

The T/2 fixed symbol timing offset is removed after the frequency/phase has been completely recovered by the Costas loop. As shown in Figure 17, the phase/frequency corrected signal gets split into a parallel I-Q data stream. The I-data is then delayed by T/2, and then recombined with the Q-data to form an offset free phase tracked QPSK signal. Because the data has been recombined, the timing tracking and match filtering blocks operate on complex I-Q data, instead of working on I-data and Q-data independently.

Another difference with Figure 16 is that the in-phase and quadrature signals require a de-interleaving block prior to their Viterbi decoding. This de-interleaving works by taking the in-phase vector  $\vec{I} = \{I_0, I_1, I_2, ...\}$ , and the quadrature vector  $\vec{Q} = \{Q_0, Q_1, Q_2, ...\}$  and combining them into a single vector,  $\vec{R} = \{I_0, Q_0, I_1, Q_1, I_2, Q_2 ...\}$ . Finally, since the EMWIN-N bits are differentially encoded, a differential decoding stage is added before the hard-decision detection at the binary slicer. After slicing, the binary data goes to the data link layer processor for header synchronization and Reed-Solomon decoding.

Figure 17. Block diagram showing the different signal processing blocks in an EMWIN OQPSK receiver.

#### 4.7 Soft-Decision Viterbi Decoder

A convolutional code is a type of error-correcting code in which each an m-bit information symbol is encoded into an n-bit symbol, where m/n is the code rate. The transformation is a function of the last k information symbols, where k is the constraint length of the code. Several algorithms exist for decoding convolutional codes. For relatively small values of k, the Viterbi algorithm is universally used as it provides maximum likelihood performance and is highly parallelizable. Viterbi decoders are thus easy to implement in digital integrated circuits and in software.

Low complexity high-throughput Viterbi decoders utilize hard-decisions to recover the information bits. However, the decoder performance suffers 3 dB loss when using hard decisions. In order to recover the 3 dB performance loss while maintaining high throughput, quantized soft-decisions are used instead of full 32-bit precision floating point numbers. Our soft-decision Viterbi decoder quantizes the 32 bit soft-decisions into 3-bit numbers (8-levels). This quantization technique allows the decoder to avoid using floating point multiplications, which significantly improves speed while still maintaining a high coding gain. Vectorized manipulation of data using the Intel Performance Primitives library also contributed to increasing the overall throughput.

The EMWIN-N, LRIT and HRIT protocols all use a rate ½ (where for each transmitted bit, an additional parity bit is transmitted) convolutional code whose parameters are described in both Table 8 and Table 10.

Viterbi decoding is more computationally intensive than all other processing blocks combined. In order to maintain a high throughput, the Viterbi decoder had to be implemented on one thread while the BPSK demodulation was implemented on a second thread. By doing this, one can take advantage of dual core CPUs, and the total system throughput is equivalent to the throughput of the slowest thread alone. Splitting the Viterbi decoder onto a separate thread is not necessary for the EMWIN-N signal due to its slow data rate.

### 4.8 EMWIN-I Signal Specifications

The EMWIN software receiver described in this section corresponds to a legacy FSK signal developed to satisfy GOES-I broadcast requirements in [22]. This data stream consists of National Weather Service (NWS) weather products and other data files. Each product or file, whether ASCII text or binary data, is divided into 1 Kbyte packets and sent as a series of asynchronous 8-bits, with no parity bits, one start and one stop bit:(8,N,1)[23]. The asynchronous bit-stream follows the RS-232 standard. This standard specifies that an 8-bit data byte is preceded by one start bit (0), and is ended with an idle sequence, which is represented by sequence of stop bits (1). As an example, consider the representation of 3 bytes of data.

A synchronous binary representation of **0** base 10, **255** base 10, and **170** base 10, is

0000000011111111110101010.

An example of an asynchronous binary representation of the same three bytes is

For easy readability, the start bits and stop bits (idle sequences) are in bold red.

There is always one start bit before every byte, however the length of the stop bit sequence (idle sequence) is indeterminate. The byte representing **0** base 10 begins with a start bit, but continues with an idle sequence of length 6, instead of just a single stop bit. After that idle time, there is a start bit, then the byte representing **255** base 10, and then a single stop bit. After that there is another start bit, the byte representing **170** base 10, and finally another idle sequence of length 3. When parsing the data for text files, the asynchronous nature of the bit-stream must be accounted for.

The EMWIN-I satellite broadcasts are transmitted as asynchronous (9600,8,N,1). The FSK signal has no formal CCSDS packet structure and no error correction codes. The signal has a rudimentary packet structure that has a header marker of 6 bytes of zeros. The header follows the same asynchronous principles as the actual data, so there is a start bit followed by an indeterminate idle sequence after each byte of zeros. Further details on the specification of this signal can be found [24].

Sometimes EMWIN-I is described as Direct FSK or DFSK, not to be confused with differential FSK. The term DFSK is obsolete and the type of modulation used by EMWIN-I is simply referred to as FSK by today's standards.

Table 11. EMWIN-I Key Parameters

| Parameter                      | Value                               |

|--------------------------------|-------------------------------------|

| Satellite Service              | GOES-11 (West), GOES-11 (East)      |

| Modulation                     | FSK                                 |

| Center Frequency               | 1690.725 MHz                        |

| Typical (140 MHz) IF Frequency | 137.225 MHz                         |

| Measured Symbol Rate           | 9600 symbols/second                 |

| Frequency Separation           | 3600 Hz                             |

| FEC                            | none                                |

| Synchronization Header         | 0x <b>00000000000</b> (hexadecimal) |

| Randomizer Polynomial          | $h(x) = 1 + x^3 + x^{20}$ (V.36)    |

### 4.9 EMWIN-I Software Receiver Architecture

Frequency-shift keying (FSK) is a modulation scheme that transmits information through discrete frequency changes of a carrier wave [25]. A binary FSK signal can be defined by two tone frequencies:  $f_0$  and  $f_1$ , corresponding to '0' and '1' bits. The demodulator is designed to support programmable tone frequencies.

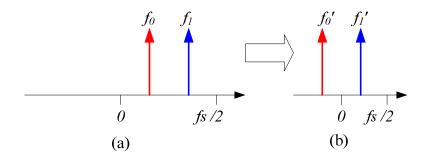

The tone frequencies may be rather large, while the symbol rate is typically very small. The Nyquist sampling [19] requirement dictates a sampling rate,  $f_s$ , of at least  $2|f_1|$  to prevent aliasing. System throughput and efficiency can be improved by translating the tones such that they are centered around DC. The translation is accomplished by first mixing the received signal with a tone at a frequency of  $f_c = 1/2(f_1 + f_0)$ . The new tones are then given by:  $f_0' = 1/2(f_0 - f_1)$  and  $f_1' = 1/2(f_1 - f_0)$ , as shown in Figure 18.

Figure 18. Down-converted FSK Frequency Diagram

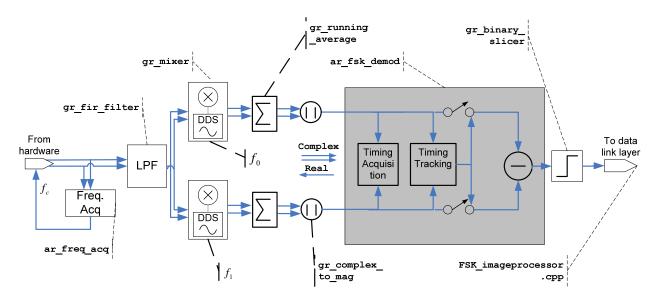

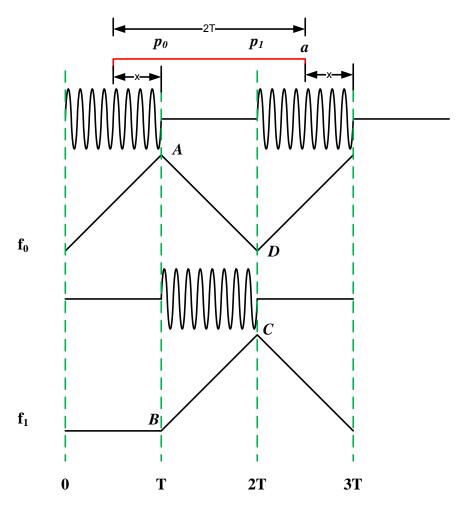

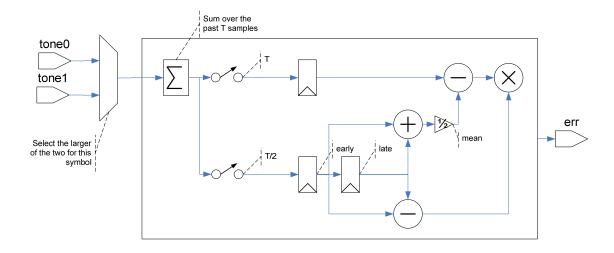

Figure 19. Block diagram showing the different signal processing blocks in an EMWIN-I FSK receiver.